Features of Synchronous

Features of Synchronous are as follows.

- construction is very simple in design.

- All the flip-flops are interconnected and will be driven by the same clock signal.

- the state output of the previous flip-flop determined the state change of the present flip-flop.

- operation is fast.

Design procedure

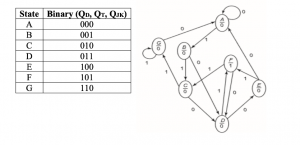

- Constructs a state diagram from the given information.

- Construct the circuit excitation table.

- Obtain the transition table from the circuit excitation table.

- Determine the number of flip-flops needed.

- Chose the type of flip-flop to be used.

- Used k-map or another simplification method to drive the circuit.

- Draw the logic diagram.

Q.N: Design a 3-bit synchronous UP counter using T-flip-flop.

Excitation table for T-flip-flop.

Transition table for T-flip-flops.

K-map simplification

K-map for TA

K-map for TB

K-map for TC

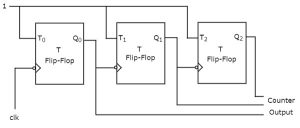

Circuit Diagram

T-flip-flop

T-flip-flop is known as toggle flip-flop. The t-flip-flop is the modification of the J-K flip-flop. T-flip-flop is obtained from J-K flip-flop by connecting both J and K together.

3-Bit Asynchronous UP Counter

A 3-bit asynchronous binary counter is shown below. The basic operation is the same as that of the 2-bit asynchronous counter. The 3-bit counters as 8 state de to kit 3 flip-flops. A timing diagram is shown below. Notice that the counter progresses through a binary count of 0 through 7 and the recycle to the 0 states.

You may also like 3-Bit Asynchronous UP Counter

Leave a Reply