Set(S)-Reset(R) Flipflop

The Set(S)-Reset(R) flipflop also knew as S-R latch can be considered as one of the most basic sequential logic circuits possible. This simple flipflop is basically one-bit memory by the stable device that has two inputs on, which will set the device (output=1) and is labeled ‘S’ on which will reset the device (the output =0) labeled ‘R’.

S-R stands for a set, reset. The reset input resets the flipflop that to its original states with an output ‘Q’ that will either at the logic label ‘1’ or logic ‘0’ depending upon the set, reset condition.

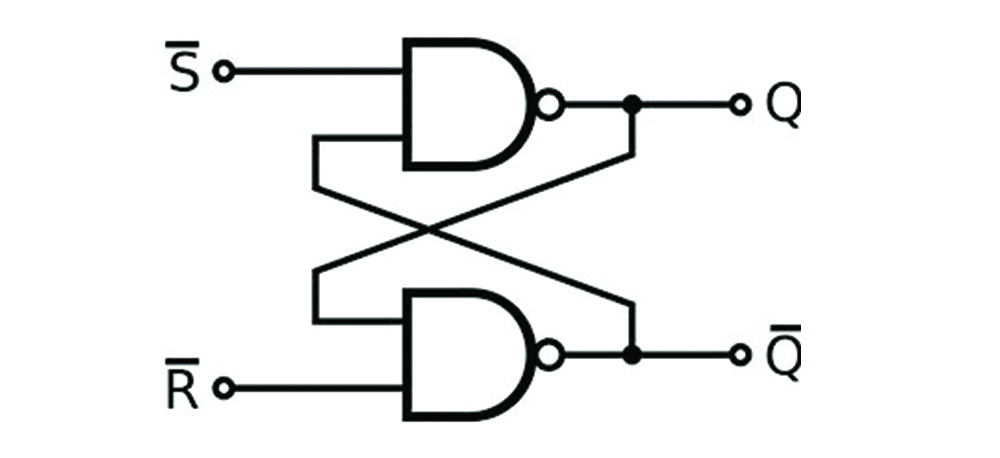

The logic circuit of S-R flipflop

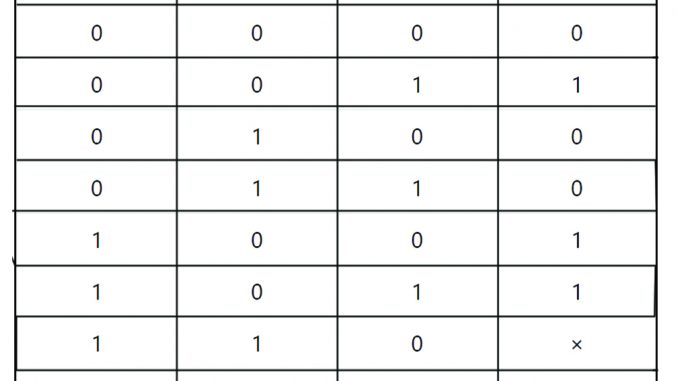

Characteristics table of S-R flipflop

The truth table of S-R NOR flipflop

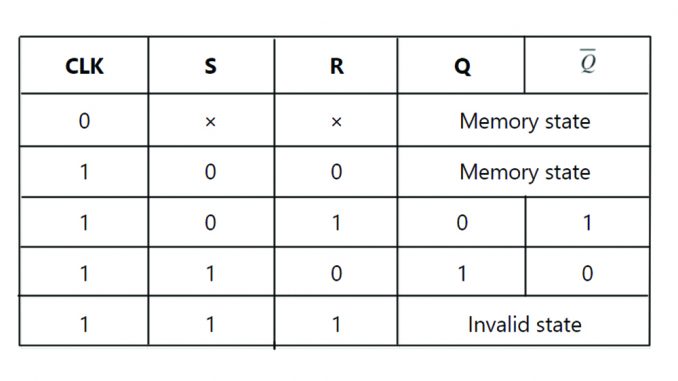

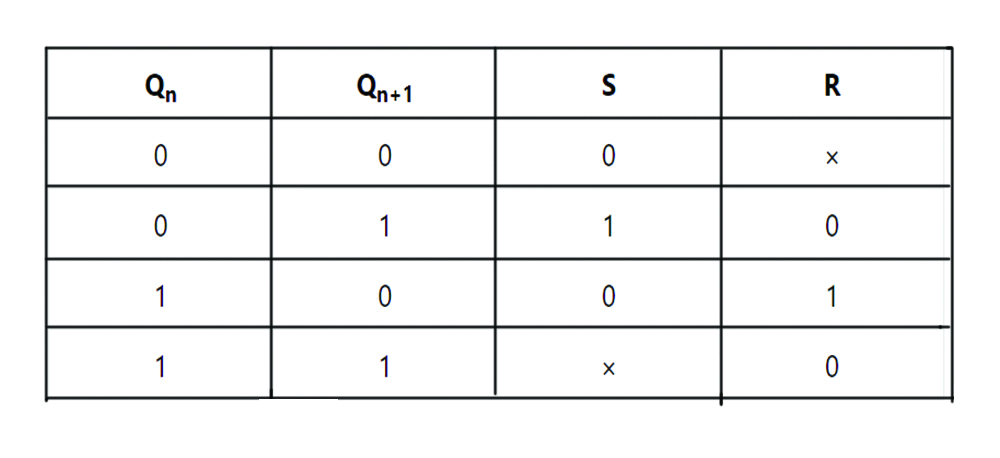

Excitation Table

The characteristics table for the flipflop show in the above table. This table summarized the operation of the flipflop on the tabular form.’Qn‘ is the binary state of a flipflop at a given time referred to the present state ‘S’ and ‘R’ column used the possible value of ‘S’ input and Qn+1 the state of flipflop after the assurance of the clock plus refer to its next step, hence next step depends upon inputs and previous step.

You may also like Code Conversion

Leave a Reply