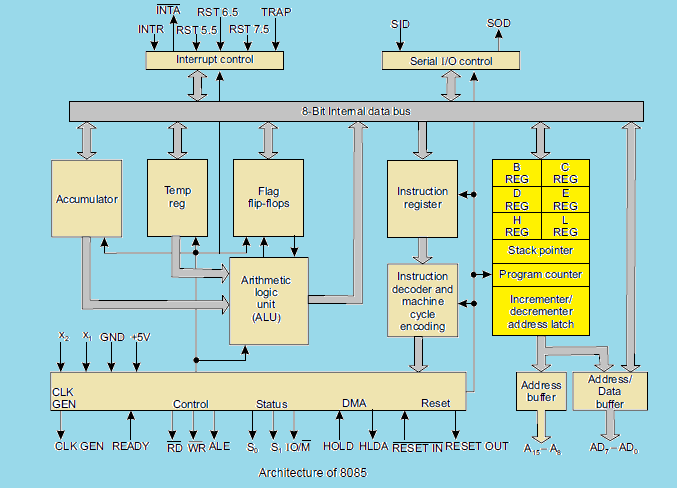

ARCHITECTURE BLOCK DIAGRAM OF 8085 MICROPROCESSOR

8085 is pronounced as an “eighty-eighty-five” microprocessor. It is an 8-bit microprocessor designed by Intel in 1977 using NMOS technology.

It has the following configuration −

- 8-bit data bus

- 16-bit address bus, which can address up to 64KB

- A 16-bit program counter

- A 16-bit stack pointer

- Six 8-bit registers arranged in pairs: BC, DE, HL

- Requires +5V supply to operate at 3.2 MHZ single-phase clock

It is used in washing machines, microwave ovens, mobile phones, etc.

8085 Microprocessor – Functional Units

8085 consists of the following functional units –

- Accumulator:- It is an 8-bit register used to perform arithmetic, logical, I/O & LOAD/STORE operations. It is connected to the internal data bus & ALU.

- Arithmetic and logic unit:- As the name suggests, it performs arithmetic and logical operations like Addition, Subtraction, AND, OR, etc. on 8-bit data.

- General-purpose register:- There are 6 general-purpose registers in 8085 processor, i.e. B, C, D, E, H & L. Each register can hold 8-bit data. These registers can work in pairs to hold 16-bit data and their pairing combination is like B-C, D-E & H-L.

- Program counter:- It is a 16-bit register used to store the memory address location of the next instruction to be executed. Microprocessor increments the program whenever an instruction is being executed so that the program counterpoints to the memory address of the next instruction that is going to be executed.

- Stack pointer:- It is also a 16-bit register that works like a stack, which is always incremented/decremented by 2 during push & pop operations.

- Temporary register:- It is an 8-bit register, which holds the temporary data of arithmetic and logical operations.

- Flag register:- It is an 8-bit register having five 1-bit flip-flops, which holds either 0 or 1 depending upon the result stored in the accumulator.

These are the set of 5 flip-flops −

- Sign (S)

- Zero (Z)

- Auxiliary Carry (AC)

- Parity (P)

- Carry (C)

Its bit position is shown in the following table:-

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| S | Z | AC | P | CY |

The bit position of the flip flop in flag register is above;

1. Sign(S)- If D7 of the result is 1 then sign flag is set otherwise reset. As we know that a number on the D7 always decides the sign of the number.

if D7 is 1: the number is negative.

if D7 is 0: the number is positive.

2. Zeros (Z)-If the result stored in an accumulator is zero then this flip flop is set otherwise it is reset.

3. Auxiliary carry (AC)-If any carry goes from D3 to D4 in the output then it is set otherwise it is reset.

4. Parity (P)-If the no of 1’s is even in the output stored in the accumulator then it is set otherwise it is reset for the odd.

5. Carry(C)-If the result stored in an accumulator generates a carry in its final output then it is set otherwise it is reset. The carry flag also serves as a borrow flag for subtraction

- Instruction register and decoder

It is an 8-bit register. When an instruction is fetched from memory then it is stored in the Instruction register. Instruction decoder decodes the information present in the Instruction register.

- Timing and control unit

It provides timing and control signals to the microprocessor to perform operations. Following are the timing and control signals, which control external and internal circuits −

- Control Signals: READY, RD’, WR’, ALE

- Status Signals: S0, S1, IO/M’

- DMA Signals: HOLD, HLDA

- RESET Signals: RESET IN, RESET OUT

- Interrupt control

As the name suggests it controls the interrupts during a process. When a microprocessor is executing the main program and whenever an interrupt occurs, the microprocessor shifts the control from the main program to process the incoming request. After the request is completed, the control goes back to the main program.

There are 5 interrupt signals in 8085 microprocessor: INTR, RST 7.5, RST 6.5, RST 5.5, TRAP.

- Serial Input/output control

It controls the serial data communication by using these two instructions: SID (Serial input data) and SOD (Serial output data).

- Address buffer and address-data buffer

The content stored in the stack pointer and program counter is loaded into the address buffer and address-data buffer to communicate with the CPU. The memory and I/O chips are connected to these buses; the CPU can exchange the desired data with the memory and I/O chips.

- Address bus and data bus

The data bus carries the data to be stored. It is bidirectional, whereas the address bus carries the location to where it should be stored and it is unidirectional. It is used to transfer the data & Address I/O devices.

FEATURES OF 8085 MICROPROCESSOR:-

- Intel 8085 is an 8-bit, N-channel Metal Oxide Semiconductor (NMOS) microprocessor

- It is a 40 pin IC package fabricated on a single Large Scale Integration (LSI) chip

- The Intel 8085 uses a single +5V DC supply for its operation

- Its clock speed is about 3MHz

- It provides 16 address lines so it can access 2^16 = 64 KB of memory

- Accumulator based

- It has 80 basic instructions, 246 op-codes, and 5 addressing modes.

- It contains 6200 transistors approx.

- Its dimensions are 164mm x 222 mm

INSTRUCTIONS AND DATA FORMAT OF 8085 MICROPROCESSOR

A microcomputer performs a task by reading and executing the set of instructions written in its memory. This set of instructions, written in a sequence is called Program.

It is a group of bits that instruct the computer to perform a specific operation.

An instruction is a command to the microprocessor to perform a given task on a specified date.

Each instruction has two parts: one is the task to be performed, called the operation code (op-code), and the second is the data to be operated on, called the operand.

8085 has 80 basic instructions, 246 op-codes.

| Opcode | Address/operands |

Fig: Instructions format

Op Code= Operation to be performed

Address = address of operand on memory

Eg: A + B

Operands = A B

Opcode = +

TYPES OF INSTRUCTION FORMATS

The 8085A instruction set consists of one, two and three-byte instructions. The first byte is always the opcode; in two-byte instructions, the second byte is usually data; in three-byte instructions the last two bytes present address or 16-bit data.

- One Byte Instruction Formats:

- Generally, the op-code & operand are 8-bit or 1 byte.

- Specifies the operation which has to be performed or who going to do that operation.

- Generally, only one byte of a memory location is required.

- Format: Op-code, In this only op-code is present

Eg: MOV B, C; Move Data; copy the content of C register to B register without modifying the content of the source register.

- Two Byte Instruction Formats:

- The first byte of two-byte instruction specifies the operation or opcode.

1 byte – Op-Code

- The second byte of the instruction specifies the operand or data.

2 byte – Operand

- Format :

| Opcode | Operands |

Eg: MVI B, 80H; MVI means immediate data. 57H is an immediate data and it is to be copied in the B register

3.Three Byte Instruction Format:

- The first byte specifies the op-code or operation

- The second and third byte of three-byte of the instruction specifies the operand.

- Generally, it used a 16-bit or 16-bit memory address location.

- II byte store the lower order 8 –bit of 16-bit operand.

- III byte store higher-order 8-bit of 16-bit operand.

D15, D14 – – – – – – D8 D7, D6 – – – – – – D0

Higher order 8-bit Lower order 8 – bit

- Format :

| Opcode | Operand | Operand |

- Eg STA , 5600H, ST = Store, A= Accumulator, 5600H = memory location

Computer Instruction: It is a sequence of binary bits that tells the computer to do some specific task.

- An instruction usually consists of Operation code and

- Sometimes instruction just consists of operation code (Opcode)

- All of the Opcodes and operands are binary codes.

- Computer instructions (Opcode and operands) are normally stored in a consecutive memory location (g. RAM) and executed sequentially one at a time.

The control reads an instruction from a specific address in memory and executes it. It then continues by reading the next instruction in sequence and execute

Eg: LD A, 01H

Here,

LD stands for Load

A stand for Accumulator

01 is Data (operands)&

H means Data is in Hexadecimal

Fig: How operation is performed inside the Processor.

Addressing Modes of 8085:-

Addressing mode is the way in which operand of the instruction is specified.

The way the operands are chosen during execution.

Types of addressing modes:-

In 8085 microprocessor there are 5 types of addressing modes:

- Immediate Addressing Mode:- In immediate addressing mode, the source operand is always data. If the data is 8-bit, then the instruction will be of 2 bytes, if the data is of 16-bit then the instruction will be of 3 bytes.

Examples:

MVI B 45 (move the data 45H immediately to register B)

LXI H 3050 (load the H-L pair with the operand 3050H immediately)

JMP address (jump to the operand address immediately)

- Register Addressing Mode:- In register addressing mode, the data to be operated is available inside the register(s) and register(s) is(are) operands. Therefore the operation is performed within various registers of the microprocessor.

Examples:

MOV A, B (move the contents of register B to register A)

ADD B (add contents of registers A and B and store the result in register A)

INR A (increment the contents of register A by one)

- Direct Addressing Mode:- Indirect addressing mode, the data to be operated is available inside a memory location and that memory location is directly specified as an operand. The operand is directly available in the instruction itself.

Examples:

LDA 2050 (load the contents of a memory location into accumulator A)

LHLD address (load contents of a 16-bit memory location into H-L register pair)

IN 35 (read the data from port whose address is 01)

- Register Indirect Addressing Mode:- In register indirect addressing mode, the data to be operated is available inside a memory location and that memory location is indirectly specified b a register pair.

Examples:

MOV A, M (move the contents of the memory location pointed by the H-L pair to the accumulator)

LDAX B (move contains B-C register to the accumulator)

LXIH 9570 (load immediate the H-L pair with the address of the location 9570)

- Implied/Implicit Addressing Mode:- In implied/implicit addressing mode the operand is hidden and the data to be operated is available in the instruction itself.

Examples:

CMA (finds and stores the 1’s complement of the contains accumulator A in A)

RRC (rotate accumulator A right by one bit)

RLC (rotate accumulator A left by one bit)

INSTRUCTIONS SET OF 8085 MICROPROCESSOR

An instruction is a command given to the computer to perform a specified operation on the given data. The instruction set of a microprocessor is the collection of the instructions that the microprocessor is designed to execute. The instruction described here is of Intel 8085. These instructions are of Intel Corporation. They cannot be used by other manufactures. The programmer can write a program in assembly language using these instructions. These instructions have been classified into the following groups:

- Data transfer (copy) Instruction

- Arithmetic Instruction

- Logical Instruction

- Branching Instruction and

- Machine control Instruction

1. DATA TRANSFER INSTRUCTION:- Data transfer instructions are the instructions which transfer data in the microprocessor. They are also called copy instructions.

Following is the table showing the list of logical instructions:

| OPCODE | OPERAND | EXPLANATION | EXAMPLE |

| MOV | Rd, Rs | Rd = Rs | MOV A, B |

| MOV | Rd, M | Rd = Mc | MOV A, 2050 |

| MOV | M, Rs | M = Rs | MOV 2050, A |

| MVI | Rd, 8-bit data | Rd = 8-bit data | MVI A, 50 |

| MVI | M, 8-bit data | M = 8-bit data | MVI 2050, 50 |

| LDA | 16-bit address | A = contents at address | LDA 2050 |

| STA | 16-bit address | contents at address = A | STA 2050 |

| LHLD | 16-bit address | directly loads at H & L registers | LHLD 2050 |

| SHLD | 16-bit address | directly stores from H & L registers | SHLD 2050 |

| LXI | r.p., 16-bit data | loads the specified register pair with data | LXI H, 3050 |

| LDAX | r.p. | indirectly loads at the accumulator A | LDAX H |

| STAX | 16-bit address | indirectly stores from the accumulator A | STAX 2050 |

| XCHG | none | exchanges H with D, and L with E | XCHG |

| PUSH | r.p. | pushes r.p. to the stack | PUSH H |

| POP | r.p. | pops the stack to r.p. | POP H |

| IN | 8-bit port address | inputs contents of the specified port to A | IN 15 |

| OUT | 8-bit port address | outputs contents of A to the specified port | OUT 15 |

In the table,

R stands for register

M stands for memory

r.p. stands for register pair

2. ARITHMETIC INSTRUCTION

Arithmetic Instructions are the instructions that perform basic arithmetic operations such as addition, subtraction and a few more. In 8085 microprocessor, the destination operand is generally the accumulator. In 8085 microprocessor, the destination operand is generally the accumulator.

Following is the table showing the list of arithmetic instructions:

| OPCODE | OPERAND | EXPLANATION | EXAMPLE |

| ADD | R | A = A + R | ADD B |

| ADD | M | A = A + Mc | ADD 2050 |

| ADI | 8-bit data | A = A + 8-bit data | ADD 50 |

| ADC | R | A = A + R + prev. carry | ADC B |

| ADC | M | A = A + Mc + prev. carry | ADC 2050 |

| ACI | 8-bit data | A = A + 8-bit data + prev. carry | ACI 50 |

| SUB | R | A = A – R | SUB B |

| SUB | M | A = A – Mc | SUB 2050 |

| SUI | 8-bit data | A = A – 8-bit data | SUI 50 |

| SBB | R | A = A – R – prev. carry | SBB B |

| SBB | M | A = A – Mc -prev. carry | SBB 2050 |

| SBI | 8-bit data | A = A – 8-bit data – prev. carry | SBI 50 |

| INR | R | R = R + 1 | INR B |

| INR | M | M = Mc + 1 | INR 2050 |

| INX | r.p. | r.p. = r.p. + 1 | INX H |

| DCR | R | R = R – 1 | DCR B |

| DCR | M | M = Mc – 1 | DCR 2050 |

| DCX | r.p. | r.p. = r.p. – 1 | DCX H |

| DAD | r.p. | HL = HL + r.p. | DAD H |

In the table,

R stands for register

M stands for memory

Mc stands for memory contents

r.p. stands for register pair

3.LOGICAL INSTRUCTION

Logical instructions are the instructions which perform basic logical operations such as AND, OR, etc. In 8085 microprocessor, the destination operand is always the accumulator. Here logical operation works on a bitwise level.

Following is the table showing the list of logical instructions:

| OPCODE | OPERAND | DESTINATION | EXAMPLE |

| ANA | R | A = A AND R | ANA B |

| ANA | M | A = A AND Mc | ANA 2050 |

| ANI | 8-bit data | A = A AND 8-bit data | ANI 50 |

| ORA | R | A = A OR R | ORA B |

| ORA | M | A = A OR Mc | ORA 2050 |

| ORI | 8-bit data | A = A OR 8-bit data | ORI 50 |

| XRA | R | A = A XOR R | XRA B |

| XRA | M | A = A XOR Mc | XRA 2050 |

| XRI | 8-bit data | A = A XOR 8-bit data | XRI 50 |

| CMA | none | A = 1’s complement of A | CMA |

| CMP | R | Compares R with A and triggers the flag register | CMP B |

| CMP | M | Compares Mc with A and triggers the flag register | CMP 2050 |

| CPI | 8-bit data | Compares 8-bit data with A and triggers the flag register | CPI 50 |

| RRC | none | Rotate accumulator right without carry | RRC |

| RLC | none | Rotate accumulator left without carrying | RLC |

| RAR | none | Rotate accumulator right with carrying | RAR |

| RAL | none | Rotate accumulator left with a carrying | RAR |

| CMC | none | Compliments the carry flag | CMC |

| STC | none | Sets the carry flag | STC |

In the table,

R stands for register

M stands for memory

Mc stands for memory contents

4. BRANCHING INSTRUCTION

Branching instructions refer to the act of switching execution to a different instruction sequence as a result of executing a branch instruction.

The three types of branching instructions are:

- Jump (unconditional and conditional)

- Call (unconditional and conditional)

- Return (unconditional and conditional)

- Jump Instructions –The jump instruction transfers the program sequence to the memory address given in the operand based on the specified flag. Jump instructions are 2 types: Unconditional Jump Instructions and Conditional Jump Instructions.

(a) Unconditional Jump Instructions: Transfers the program sequence to the described memory address.

| OPCODE | OPERAND | EXPLANATION | EXAMPLE |

| JMP | address | Jumps to the address | JMP 2050 |

(b) Conditional Jump Instructions: Transfers the program sequence to the described memory address only if the condition is satisfied.

| OPCODE | OPERAND | EXPLANATION | EXAMPLE |

| JC | address | Jumps to the address if the carry flag is 1 | JC 2050 |

| JNC | address | Jumps to the address if the carry flag is 0 | JNC 2050 |

| JZ | address | Jumps to the address if zero flags are 1 | JZ 2050 |

| JNZ | address | Jumps to the address if zero flags are 0 | JNZ 2050 |

| JPE | address | Jumps to the address if parity flag is 1 | JPE 2050 |

| JPO | address | Jumps to the address if parity flag is 0 | JPO 2050 |

| JM | address | Jumps to the address if sign flag is 1 | JM 2050 |

| JP | address | Jumps to the address if sign flag 0 | JP 2050 |

- Call Instructions –The call instruction transfers the program sequence to the memory address given in the operand. Before transferring, the address of the next instruction after CALL is pushed onto the stack. Call instructions are 2 types: Unconditional Call Instructions and Conditional Call Instructions.

(a) Unconditional Call Instructions: It transfers the program sequence to the memory address given in the operand.

| OPCODE | OPERAND | EXPLANATION | EXAMPLE |

| CALL | address | Unconditionally calls | CALL 2050 |

(b) Conditional Call Instructions: Only if the condition is satisfied, the instructions execute.

| OPCODE | OPERAND | EXPLANATION | EXAMPLE |

| CC | address | Call if the carry flag is 1 | CC 2050 |

| CNC | address | Call if the carry flag is 0 | CNC 2050 |

| CZ | address | Calls if zero flags are 1 | CZ 2050 |

| CNZ | address | Calls if zero flags are 0 | CNZ 2050 |

| CPE | address | Calls if the carry flag is 1 | CPE 2050 |

| CPO | address | Calls if the carry flag is 0 | CPO 2050 |

| CM | address | Calls if sign flag is 1 | CM 2050 |

| CP | address | Calls if sign flag is 0 | CP 2050 |

- Return Instructions –The return instruction transfers the program sequence from the subroutine to the calling program. Jump instructions are 2 types: Unconditional Jump Instructions and Conditional Jump Instructions.

(a) Unconditional Return Instruction: The program sequence is transferred unconditionally from the subroutine to the calling program.

| OPCODE | OPERAND | EXPLANATION | EXAMPLE |

| RET | none | Return from the subroutine unconditionally | RET |

(b) Conditional Return Instruction: The program sequence is transferred unconditionally from the subroutine to the calling program only is the condition is satisfied.

| OPCODE | OPERAND | EXPLANATION | EXAMPLE |

| RC | none | Return from the subroutine if the carry flag is 1 | RC |

| RNC | none | Return from the subroutine if the carry flag is 0 | RNC |

| RZ | none | Return from the subroutine if zero flags are 1 | RZ |

| RNZ | none | Return from the subroutine if zero flags are 0 | RNZ |

| RPE | none | Return from the subroutine if parity flag is 1 | RPE |

| RPO | none | Return from the subroutine if parity flag is 0 | RPO |

| RM | none | Returns from the subroutine if sign flag is 1 | RM |

| RP | none | Returns from the subroutine if sign flag is 0 | RP |

You may also like Pin Configuration of 8085 microprocessor

Hello there, I found your website via Google while searching for a related topic, your website came up, it looks great. I have bookmarked it in my google bookmarks.

My programmer is trying to convince me to move to .net from PHP. I have always disliked the idea because of the costs. But he’s tryiong none the less. I’ve been using WordPress on numerous websites for about a year and am nervous about switching to another platform. I have heard good things about blogengine.net. Is there a way I can import all my wordpress posts into it? Any help would be really appreciated!

Just wish to say your article is as astounding. The clearness in your post is simply spectacular and i can assume you’re an expert on this subject. Well with your permission let me to grab your RSS feed to keep updated with forthcoming post. Thanks a million and please carry on the enjoyable work.