Interrupt Processing Sequence

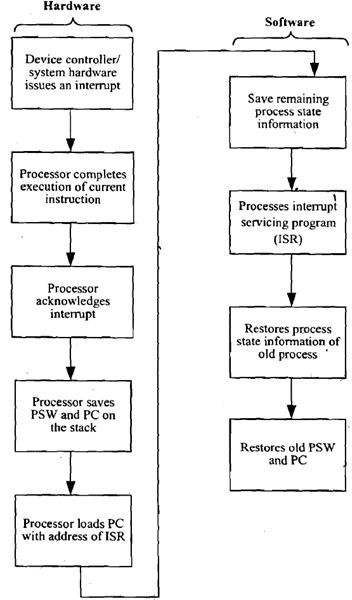

The occurrence of an interrupt fires a number of events both in processor hardware and software. The figure below displays a sequence.

The occurrence of interrupt triggers a number of events, both in processor hardware and in

software. The interrupt-driven I/O operation takes the following steps.

- The I/O unit issues an interrupt signal to the processor for the exchange of data between

them. - The processor finishes the execution of the current instruction before responding to the

interrupt. - The processor sends an acknowledgment signal to the device that it issued the interrupt.

- The processor transfers its control to the requested routine called “Interrupt Service

Routine (ISR)” by saving the contents of program status word (PSW) and the program

counter (PC). - The processor now loads the PC with the location of interrupt service routine and the

fetches the instructions. The result is transferred to the interrupt handler program. - When interrupt processing is completed, the saved register’s value is retrieved from the

stack and restored to the register. - Finally, it restores the PSW and PC values from the stack.

Interrupt priority:

Microcomputers can transfer data to or from an external device using interrupt through INTR pin. When a device wants to communicate with the microcomputer, it connects to the INTR pin and makes it high or low depending on a microcomputer. The microcomputer responds by sending a signal via its pin called interrupt acknowledgment INTA.

You may also like I/O Address Decoding

Leave a Reply